Das Konzept

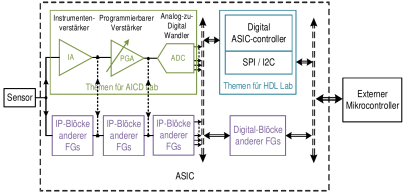

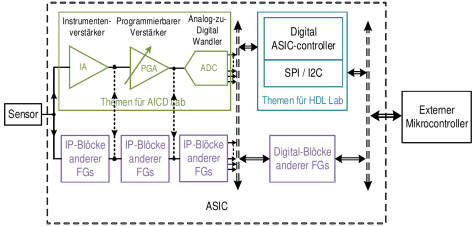

Integrierte elektronische Systeme nehmen in der heutigen Zeit immer mehr an Bedeutung und Komplexität zu. Dabei arbeiten IngenieurInnen arbeitsteilig zusammen, wobei nach wohl definierten Spezifikationen IP-Blöcke erstellt werden. Durch Zusammensetzten vieler individuellen Blöcke ergibt sich der ASIC.

Wir am Fachbereich wollen den Chipentwurf möglichst praxisnah abbilden, um den Studierenden bestmöglich auf spätere Tätigkeiten im Bereich der Halbleiterentwicklungen vorzubereiten. Die Stationen des Entwicklungsvorgang von anfänglichen Spezifikationen bis zu einem gefertigten funktionsfähigen Chip bilden wir mit unseren vielfältigen Lehrveranstaltungen ab.

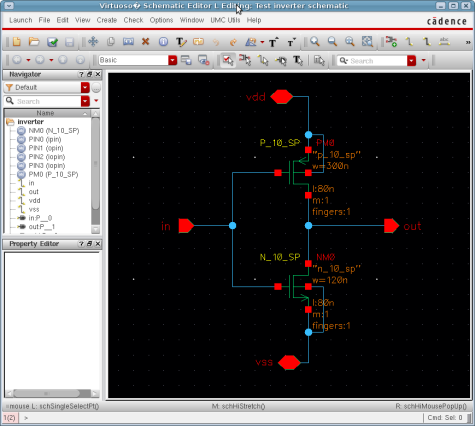

Erstellung, Simulation und Verifikation von analoger und digitalen Schaltungen werden im AICD Lab und HDL Lab durchgeführt. Die Designs werden dabei soweit ausgereift, dass sie alle Anforderungen für eine Herstellung erfüllen. Im Rahmen von Seminaren können die Studierenden anschließend die extern gefertigten Chips testen. Dafür werden spezielle Testplatinen gefertigt und die Chips im Labor vermessen.

Der Chip

Die enorme Komplexität heutiger hochmoderner integrierter Schaltungen, basierend auf jahrzehntelanger Erfahrungen von zahlreichen Ingenieurteams, lässt sich nicht schwer erreichen. Dennoch wollen wir mehr als eine rein akademische Übung bieten. Wir ermöglichen das Zusammenspiel von analoger und digitaler Schaltung mit Software für eine realitätsnahe Designaufgabe.

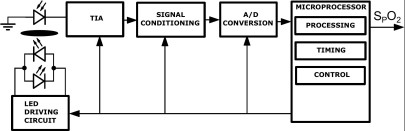

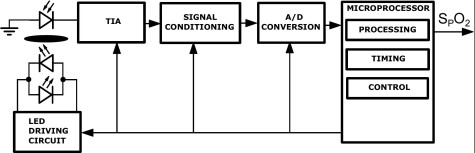

Als Motivation dient das bereits im Medizintechnik-Praktikum verwendete Verfahren der Pulsoxymetrie. Dabei können die Studierenden mittels LED‘s ungefährlich ihren Puls messen. Anstatt eines diskreten Aufbaus wie er im Medizintechnik-Praktikum verwendet wird, streben wir einen integrierten Aufbau an, der alle relevanten Funktionen auf weniger als 1 mm2 Chipfläche vereint. Jedoch lässt sich die Hardware allgemein auch für verschiedenste Sensorsignale verwenden.

Auf dem Chip führen wir die Werke von Studierenden aus verschiedenen Veranstaltungen zum Gesamtsystem zusammen. Die analogen IP-Blöcke werden im Rahmen des AICD Labs entwickelt. Diese bereiten ein analoges Sensorsignal auf und wandeln es in eine digitale Repräsentation um. Die digitalen IP-Blöcke werden im Rahmen des HDL Labs entwickelt. Diese werten das digitalisierte Eingangssignal aus um daraus Informationen wie den Puls und die Sauerstoffsättigung zu extrahieren.

AICD Lab

Für die analoge Signalkette werden drei IP-Blöcke definiert. Im Rahmen des AICD Labs entwickeln die Studierenden in Zweiergruppen je einen dieser IP_Blöcke nach Wahl.

Das Eingangssignal wird dabei zuerst durch einen Programmable Gain Amplifier (PGA) verstärkt. Dabei kann die Verstärkung in 3dB Schritten durch den digital Teil eingestellt werden und ein aktiver Anti-aliasing Filter zugeschaltet werden. Eine Bandgap-Referenz stellt eine stabile und genaue Referenzspannung bereit, um eine analog zu digital Wandlung zu ermöglichen. Mit Hilfe dieser Referenzspannung digitalisiert einen 8-bit SAR-ADC das durch den programmable gain amplifier verstärkte analoge Sensor-Signal. Die dadurch zur Verfügung gestellte digitale Repräsentation des Eingangsignal wird für weitere digitale Schaltungen zur Verfügung gestellt. Gleichzeitig lässt sich die analoge Signalkette durch Einstellen der Verstärkung anpassen.

Das Eingangssignal wird dabei zuerst durch einen Programmable Gain Amplifier (PGA) verstärkt. Dabei kann die Verstärkung in 3dB Schritten durch den digital Teil eingestellt werden und ein aktiver Anti-aliasing Filter zugeschaltet werden. Eine Bandgap-Referenz stellt eine stabile und genaue Referenzspannung bereit, um eine analog zu digital Wandlung zu ermöglichen. Mit Hilfe dieser Referenzspannung digitalisiert einen 8-bit SAR-ADC das durch den programmable gain amplifier verstärkte analoge Sensor-Signal. Die dadurch zur Verfügung gestellte digitale Repräsentation des Eingangsignal wird für weitere digitale Schaltungen zur Verfügung gestellt. Gleichzeitig lässt sich die analoge Signalkette durch Einstellen der Verstärkung anpassen.

HDL Lab

Im HDL Lab wird der digitale Designflow für das Pulsoximeter durchgeführt.

Dafür werden verschiedene Schaltungsblöcke wie zum Beispiel ein FIR Filter oder die digitale Steuerungseinheit in Verilog (Hardware Description Language-Lab) entwickelt. Der FIR Filter entfernt dabei die hochfrequenten Anteile des Eingangsignals. Die digitale Steuerungseinheit übernimmt dabei die Steuerung von verschiedenen im AICD Lab entwickelten Schaltungsblöcken wie zum Beispiel den programmable gain amplifier (PGA) und SAR-ADC.

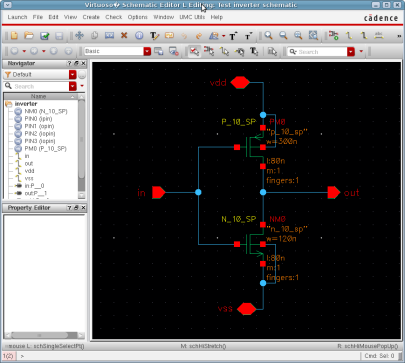

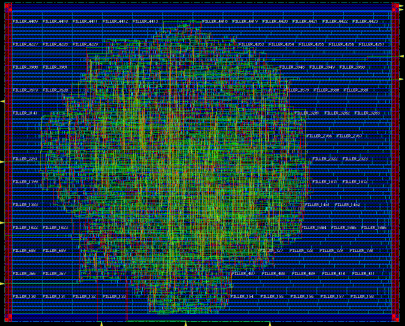

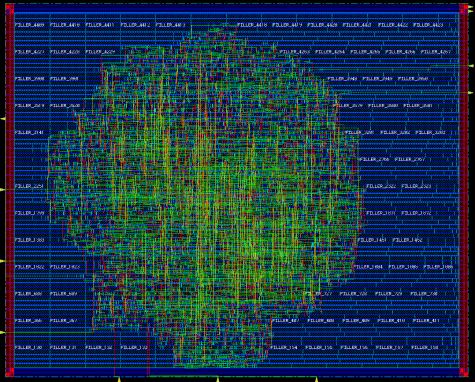

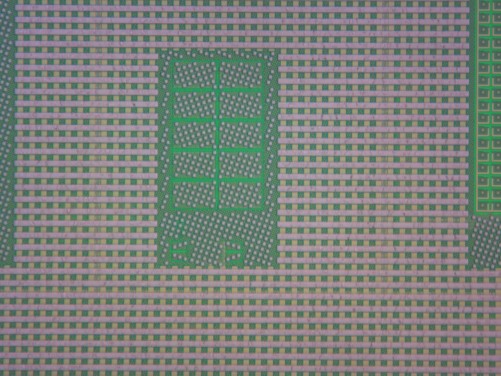

Bei der Entwicklung muss der geschriebene Code von den Studierenden in verschiedenen Testbenches verifiziert werden. Dabei werden auch mixed signal simulationen (AMS) durchgeführt, um sicherzustellen das der entworfene Analogteil aus dem AICD Lab auch mit dem im HDL Lab geschrieben Verilog Code einwandfrei funktioniert. Bei erfolgreicher Verifizierung wird der Verilog Code mit Synopsys Design Vision synthetisiert. Dabei wird der geschriebene Verilog Code in einen Schaltplan mit Logik Gattern übersetzt. Nach erfolgreicher Synthese wird das Place and Route mit Cadence Encounter durchgeführt. In diesem Schritt wird der zuvor generierte Schaltplan mit Logik Gattern in ein physisches Layout überführt.

Tapeout

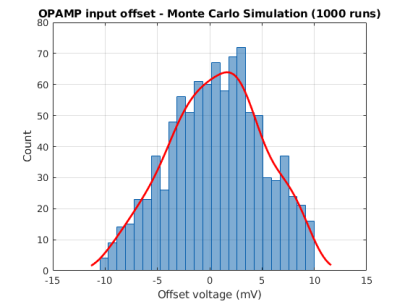

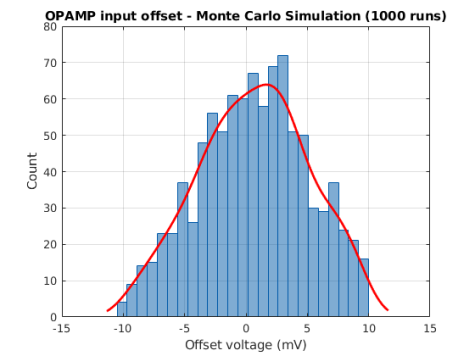

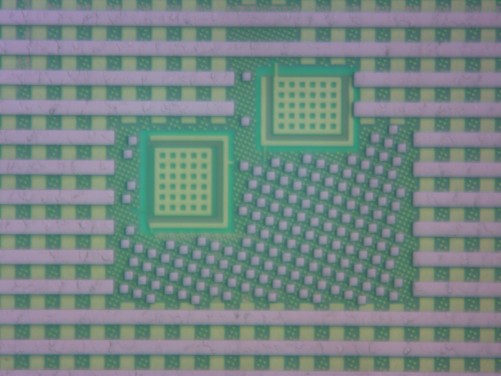

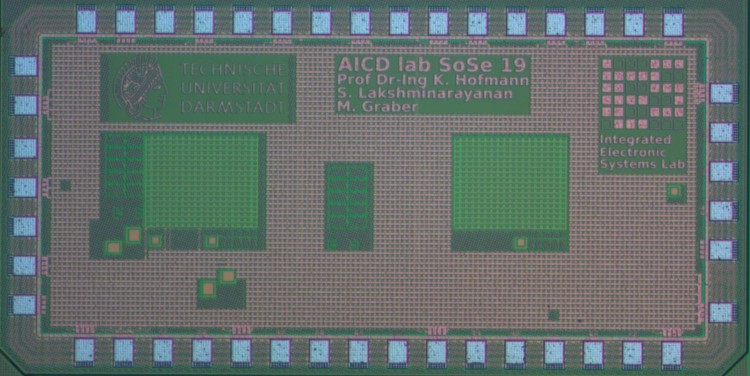

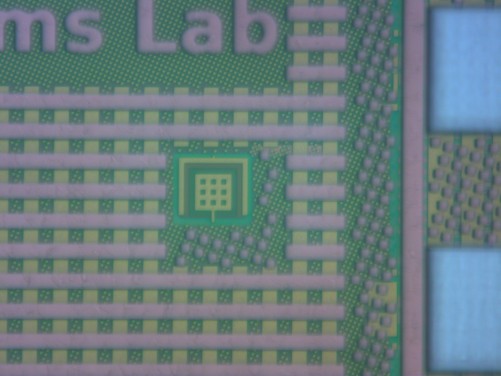

Im Anschluss an die Vorlesungszeit werden die Chips gefertigt. Die Designs werden ausführlich Post-layout simuliert um diese auf Robustheit bei Herstellungsungenauigkeiten zu testen. Der hier abgebildeten Chip beleget weniger als 1 mm2 Fläche, wobei die Größe der eigentlichen Schaltung deutlich kleiner ist. Zusätzliche Strukturen wie IO-Zellen mit ESD Schutz und Pads für die elektrische Kontaktierung werden hinzugefügt. Unter dem Mikroskop lässt sich der Chip schön mit den Layout Daten Vergleichen.

Labormessungen

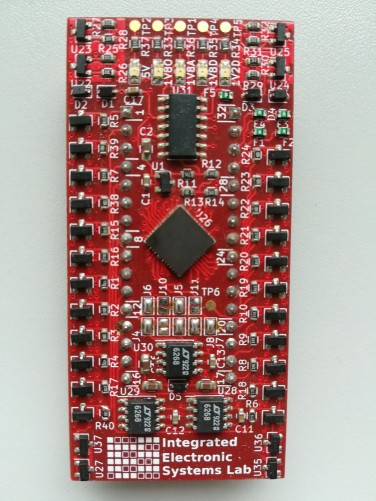

Die gefertigten Chips können anschließend in unserem Labor vermessen werden. Als erster Schritt wird eine Platine gefertigt, die den Chip mit Spannung versorgt und Steckverbinder zum Anschluss. Für Messungen ist der Umgang mit Labormessgeräten wie beispielsweise Oszilloskop, Funktionsgenerator und Labornetzgerät notwendig. Darüber hinaus gehört eine Nachbearbeitung und Auswertung zum festen Bestandteil. Die erhaltene Messwerte können mit den simulierten Werten verglichen werden und Ursachen für Abweichungen identifiziert werden.

Plattform für weitere Designs

Die am IES entwickelten Schaltungen belegen nur einen kleinen Teil der zur Verfügung stehenden Chipfläche in der verwendeten UMC 65nm low leakage Technologie. Ein großer Teil der Fläche ist nur mit einem Power Grid und Fillern versehen um die Herstellungs-konforme Lösung zu erhalten.

Daher besteht die Möglichkeit für andere hessische Hochschulen/Universitäten eigene Schaltungsteile hinzuzufügen. Diese können unsere bestehende Schaltungen mitbenutzten oder mittels eigener IO Pads unabhängig zu arbeiten. Für Anfragen diesbezüglich wenden Sie sich bitte an Prof. Dr.-Ing. Klaus Hofmann.